【产业特报】奈米制程领军 带动IC产业 独步全球

摩尔定律(英语:Moore's law)是由英特尔(Intel)创始人之一戈登·摩尔提出来的。其内容为:积体电路上可容纳的电晶体(晶体管)数目,约每隔两年便会增加一倍;经常被参照的「18个月」,是由英特尔执行长大卫·豪斯(David House)所说:预计18个月会将晶片的效能提高一倍(即更多的电晶体使其更快)。(资料来源:维基百科)

而奈米制程是什么,以14奈米为例,其制程是指在芯片中,线最小可以做到14奈米的尺寸,下图为传统晶体管长相,以此作为例子。缩小晶体管的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?下图中的L就是我们期望缩小的部分。借助闸极长度,电流可以用更短的路径从Drain端到Source端。(资料来源:网路整理)

摩尔定律出现的重大突破。半导体设备厂艾斯摩尔(ASML)确认1.5奈米制程的发展性,支撑摩尔定律延续至2030年。摩尔定律未亡,至少EUV光刻工艺还可用15年。半导体制造工艺进入10nm之后,难度越来越大。为此,Intel多次调整了产品策略,10nm工艺的产品推迟到2019年,以致于很多人认为摩尔定律将死。当7nm工艺节点将开始采用ASML开发EUV光刻工艺,这将会支持未来15年半导体制造业。ASML表示,部分客户已经在讨论2030年的1.5nm工艺路线图了。(资料来源:资讯产业资讯室)

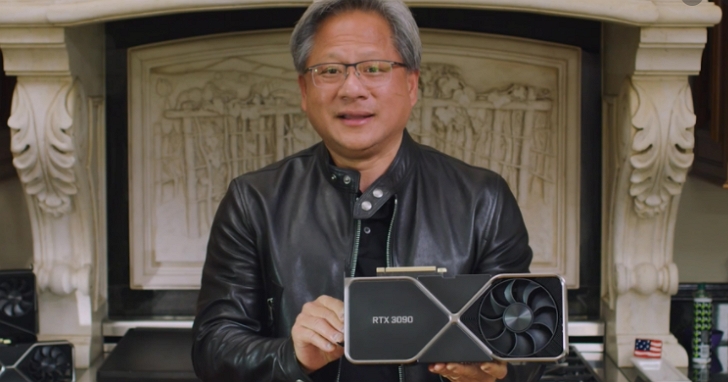

台积电7奈米制程,预期今年将有50个以上的设计案投片(tap ),包括CPU、GPU、AI加速器晶片、加密货币采矿ASIC、网路晶片、游戏机晶片、5G晶片以及车用IC。该制程节点与两个世代前的16FF+制程相较,能提供35%的速度提升或节省65%耗电,闸极密度则能提升三倍。

(资料来源:eettaiwan)

而随著人工智慧边缘运算、AI/HPC巨量资料运算、比特币挖矿运算、先进驾驶辅助系统(ADAS)及自驾车等新应用的蓬勃发展,半导体市场也出现新的典范转移,过去几年晶片需求集中在智慧型手机供应链,但今年以来已经看到很大的改变。同时,IC设计提供通用标准型晶片(ASSP)的商业模式也持续受到挑战,转而代之的是以系统厂为主的ASIC市场正在快速起飞。

(资料来源:工商时报)

马上加入粉丝专业

【华南好神资讯】 http://bit.ly/1U6NIzt

【华南永昌赛博格】https://goo.gl/isaSNu

https://www.instagram.com/